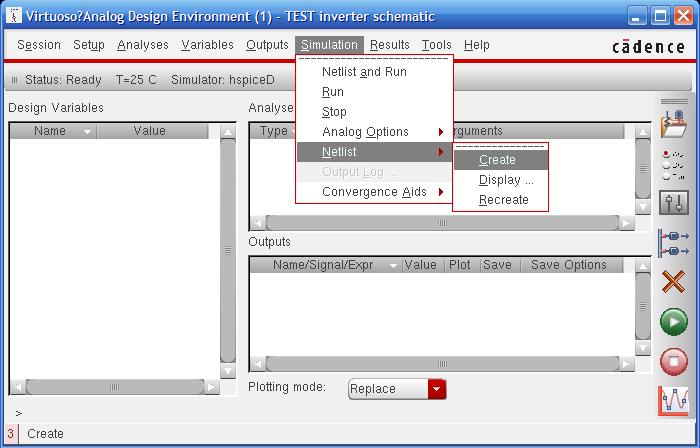

The designed projects may lead to Fabrication of test chips. All the projects (~12-15)Īre implemented using Cadence design tools including Virtuoso, Diva or Calibre DRC/LVS/Extraction and SoC encounter (for Auto Place/Route).

#Cadence vlsi design tips verification

ECE 6414 (Analog Integrated System Design): Custom IC and Verification are utilized for projects involving deep brain stimulation, wireless cardiac monitoring and electrocardiogram monitoring.ECE 6133 (Physical Design Automation VLSI Systems): Encounter and Virtuoso for digital IC designs.A significant number of students in this class also uses Spectre simulation environment for design while a fraction of students uses HSPICE for simulations. IBM130nm, FreePDK45nm etc.) with aggressive voltage/frequency targets (~1GHZ at 0.8-1V supply). The design is performed at advanced technology nodes (e.g. For example, in last two years in the design project students are designing a three stage pipelined system – an SRAM array, a one-cycle Interconnect, and a fast adder – using Cadence tools in this course.

The course uses Cadence Virtuoso as the only acceptable tool for a semester long design project in this course.

ECE 3042 and ECE 3043 use version 16.6 of SPB/Orcadlite/PSpice for basic instruction in SPICE.

#Cadence vlsi design tips software

Georgia Institute of Technology School of Electrical and Computer Engineering Cadence University Program Member Cadence Tools in the ECE CurriculumĬadence software is being used primarily in the following courses in the School of Electrical and Computer Engineering at Georgia Tech:

0 kommentar(er)

0 kommentar(er)